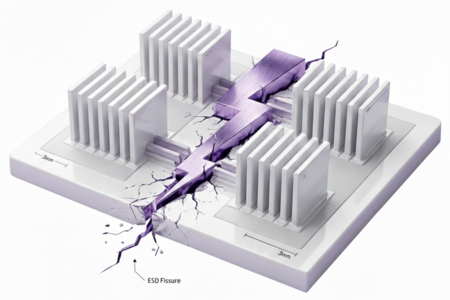

微縮化時代的無形殺手

當製程跨入3nm世代,100V的靜電足以造成毀滅性打擊

|

|

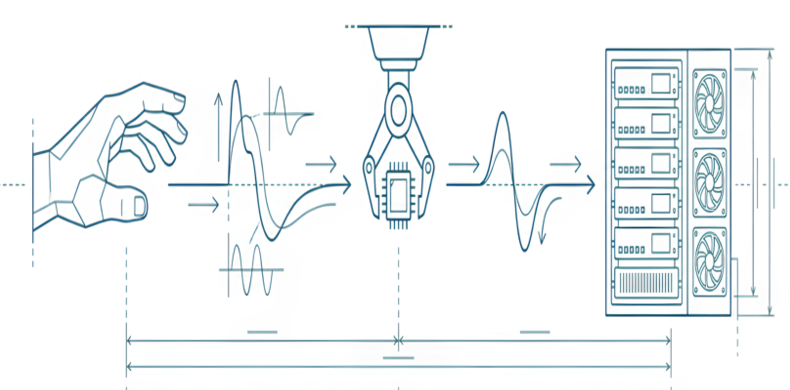

構建可靠性的衡量標尺

從人體接觸到自動化產線,我們精準模擬每一種威脅

|

||

| HBM(人體放電模式) 模擬人體移動積累電荷後的接觸。商業晶片標準需達2000V耐受度。 |

CDM(元件充電模式) 自動化產線的頭號殺手。模擬元件摩擦帶電後的瞬間放電(脈衝<1ns),電流峰值極高。 |

系統級測試(IEC 61000-4-2) 模擬終端產品在運行中面臨的嚴苛環境,確保系統不當機。 |

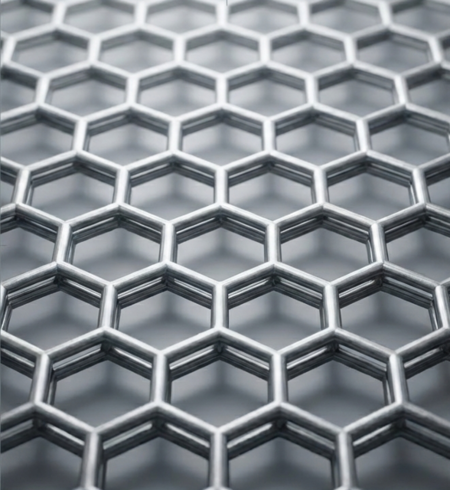

第一道防線:材料革命

離散碳奈米管(Discrete CNT)-消除傳統材料的「局部熱點」

|

|

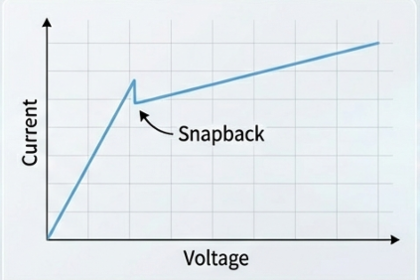

晶片端(On-Chip)的智能攔截

比功能電路更快的響應速度,在毫秒間化解危機

|

||

| 二極體與GGNMOS 利用「驟回」(Snapback)特性,在極小面積下引導大電流。 |

SCR(矽控整流器) 單位面積防護效率最高,低維持電壓防止過熱燒毀。 |

高速傳輸守護 針對USB4或5G通訊,採用低電容設計(如STSCR),確保信號零失真。 |

高壓與車用環境的極限挑戰

為200V以上的運作環境,打造精確的電位鉗制

|

|

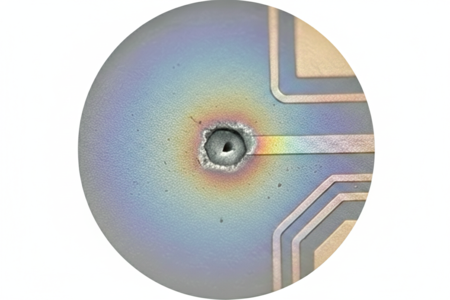

失效分析:通往完美的藍圖

透過TLP測試與數據反饋,將每一次失效轉化為設計優化

|

||

| 透視損傷機制 精確識別接面燒毁(Junction Burnout)與氧化層擊穿(Oxide Punchthrough) 。 |

TLP傳輸線脈衝測試 在奈秒級別下觀測I-V曲線,確認二次崩潰電流(It2)極限。 |

佈局優化 依據數據調整閘極間距或增加護環(Guard Ring),防止鎖死效應(Latch-up) 。 |

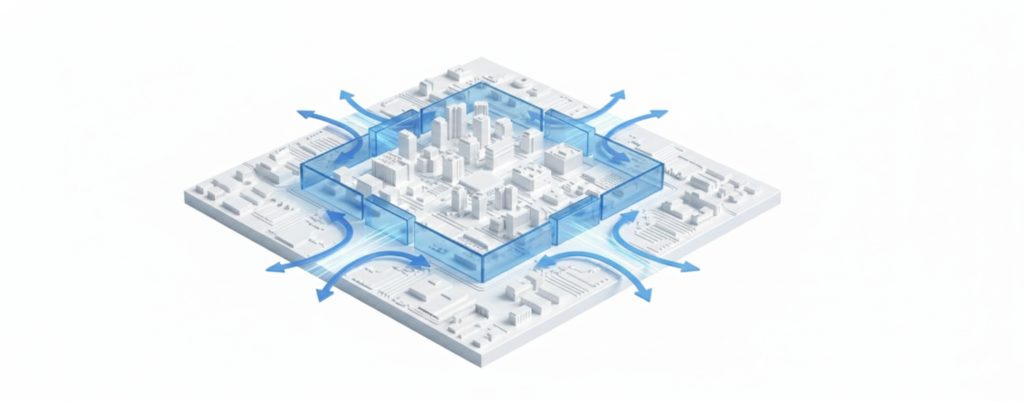

可靠性:永續經營的基石

結合先進材料、精巧設計與嚴謹標準的ESD全方位解決方案

|

|||

| 材料(Materials) CNT治具降低製造環境靜電。 |

設計 (Design) 低電容、高強度的晶片端防護。 |

標準(Standards) 接軌國際規範,確保全球市場適配性。 |

承諾(Promise) 我們不僅減少失效成本,更為您 的品牌提供最穩固的質量承諾。 |